2.5. Функції пристроїв магістралі

Розглянемо тепер, як взаємодіють на магістралі основні пристрої мікропроцесорної системи: процесор, пам'ять (оперативна і постійна), пристрої вводу/виводу.

2.5.1. Функції процесора

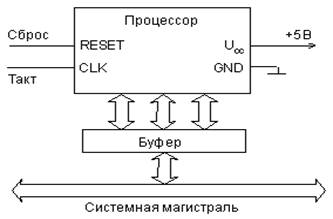

Процесор (мал. 2.16) звичайно є окремою мікросхемою або ж частиною мікросхеми (у разі мікроконтролера). В колишні роки процесор іноді виконувався на комплектах з декількох мікросхем, але зараз від такого підходу вже практично відмовилися. Мікросхема процесора обов'язково має виводи трьох шин: шини адреси, шини даних і шини управління. Іноді деякі сигнали і шини мультиплексуються, щоб зменшити кількість виводів мікросхеми процесора.

Найважливіші характеристики процесора - ця кількість розрядів його шини даних, кількість розрядів його шини адреси і кількість управляючих сигналів в шині управління. Розрядність шини даних визначає швидкість роботи системи. Розрядність шини адреси визначає допустиму складність системи. Кількість ліній управління визначає різноманітність режимів обміну і ефективність обміну процесора з іншими пристроями системи.

Окрім виводів для сигналів трьох основних шин процесор завжди має вивід (або два виводи) для підключення зовнішнього тактового сигналу або кварцового резонатора (CLK), оскільки процесор завжди є тактованим пристроєм. Чим більше тактова частота процесора, тим він швидше працює, тобто тим швидше виконує команди. Втім, швидкодія процесора визначається не тільки тактовою частотою, але і особливостями його структури. Сучасні процесори виконують більшість команд за один такт і мають засоби для паралельного виконання декількох команд. Тактова частота процесора не зв'язана прямо і жорстко із швидкістю обміну по магістралі, оскільки швидкість обміну по магістралі обмежена затримками розповсюдження сигналів і спотвореннями сигналів на магістралі. Тобто тактова частота процесора визначає тільки його внутрішню швидкодію, а не зовнішню. Іноді тактова частота процесора має нижню і верхню межі. При перевищенні верхньої межі частоти можливий перегрів процесора, а також збої, причому, що найнеприємніше, виникаючі не завжди і нерегулярно. Отже із зміною цієї частоти треба бути дуже обережним.

Мал. 2.16. Схема включення процесора.

Ще один важливий сигнал, який є в кожному процесорі, - це сигнал початкового скидання RESET. При включенні живлення, при аварійній ситуації або зависанні процесора подача цього сигналу приводить до ініціалізації процесора, примушує його приступити до виконання програми початкового запуску. Аварійна ситуація може бути викликана перешкодами по ланцюгах живлення і «землі», збоями в роботі пам'яті, зовнішніми іонізуючими випромінюваннями і іншими роичинами. В результаті процесор може втратити контроль над виконуваною програмою і зупинитися на якійсь адресі. Для виходу з цього стану якраз і використовується сигнал початкового скидання. Цей же вхід початкового скидання може використовуватися для сповіщення процесора про те, що напруга живлення стала нижче за встановлену межу. У такому разі процесор переходить до виконання програми збереження важливих даних. По суті, цей вхід є особливим різновидом радіального переривання.

Іноді у мікросхеми процесора є ще один-два входи радіальних переривань для обробки особливих ситуацій (наприклад, для переривання від зовнішнього таймера).

Шина живлення сучасного процесора звичайно має одну напругу живлення (+5В або +3,3В) і загальний дріт («землю»). Перші процесори нерідко вимагали декількох напруг живлення. В деяких процесорах передбачений режим зниженого енергоспоживання. Взагалі, сучасні мікросхеми процесорів, особливо з високими тактовими частотами, споживають досить велику потужність. В результаті для підтримки нормальної робочої температури корпусу на них нерідко доводиться встановлювати радіатори, вентилятори або навіть спеціальні мікрохолодильники.

Для підключення процесора до магістралі використовуються буферні мікросхеми, що забезпечують, якщо необхідно, демультиплексування сигналів і електричну буферизацію сигналів магістралі. Іноді протоколи обміну по системній магістралі і по шинах процесора не співпадають між собою, тоді буферні мікросхеми ще і погоджують ці протоколи один з одним. Іноді в мікропроцесорній системі використовується декілька магістралей (системних і локальних), тоді для кожної з магістралей застосовується свій буферний вузол. Така структура характерна, наприклад, для персональних комп'ютерів.

Після включення живлення процесор переходить на першу адресу програми початкового пуску і виконує цю програму. Дана програма заздалегідь записана в постійну (енергонезалежну) пам'ять. Після завершення програми початкового пуску процесор починає виконувати основну програму, що знаходиться в постійній або оперативній пам'яті, для чого вибирає по черзі всі команди. Від цієї програми процесор можуть відволікати зовнішні переривання або запити на ПДП. Команди з пам'яті процесор вибирає за допомогою циклів читання по магістралі. При необхідності процесор записує дані в пам'ять або в пристрої вводу/виводу за допомогою циклів запису або ж читає дані з пам'яті або з пристроїв вводу/виводу за допомогою циклів читання.

Таким чином, основні функції будь-якого процесора наступні:

- вибірка (читання) виконуваних команд;

- ввід (читання) даних з пам'яті або пристрою вводу/виводу;

- вивід (запис) даних в пам'ять або в пристрої вводу/виводу;

- обробка даних (операндів), у тому числі арифметичні операції над ними;

- адресація пам'яті, тобто задання адреси пам'яті, з якою проводитиметься обмін;

- обробка переривань і режиму прямого доступу.

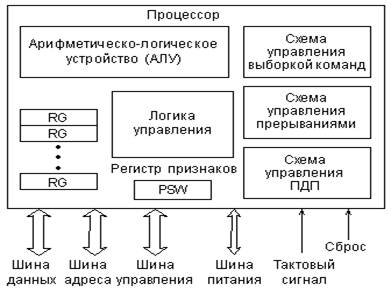

Спрощено структуру мікропроцесора можна представити в наступному вигляді (мал. 2.17).

Мал. 2.17. Внутрішня структура мікропроцесора.

Основні функції показаних вузлів наступні.

Схема управління вибіркою команд виконує читання команд з пам'яті і їх дешифрацію. В перших мікропроцесорах було неможливе одночасне виконання попередньої команди і вибірка наступної команди, оскільки процесор не міг суміщати ці операції. Але вже в 16-розрядних процесорах з'являється так званий конвейєр (черга) команд, що дозволяє вибирати кілька наступних команд, поки виконується попередня. Два процеси йдуть паралельно, що прискорює роботу процесора. Конвейєр є невеликою внутрішньою пам'яттю процесора, в яку при щонайменшій нагоді (при звільненні зовнішньої шини) записується декілька команд, наступних за виконуваною. Читаються ці команди процесором в тому ж порядку, що і записуються в конвейєр (це пам'ять типа FIFO, First In - First, перший ввійшов - перший вийшов). Правда, якщо виконувана команда припускає перехід не на наступний елемент пам'яті, а на видалену (з меншою або більшою адресою), конвейєр не допомагає, і його доводиться обнуляти. Але такі команди зустрічаються в програмах порівняно рідко.

Розвитком ідеї конвейєра стало використання внутрішньої кеш-пам'яті процесора, яка заповнюється командами, поки процесор зайнятий виконанням попередніх команд. Чим більше об'їм кеш-пам'яті, тим менше вірогідність того, що її вміст доведеться скинути при команді переходу. Зрозуміло, що обробляти команди, що знаходяться у внутрішній пам'яті, процесор може набагато швидше, ніж ті, які розташовані в зовнішній пам'яті. В кеш-пам'яті можуть зберігатися і дані, які обробляються в даний момент, це також прискорює роботу. Для більшого прискорення вибірки команд в сучасних процесорах застосовують поєднання вибірки і дешифрації, одночасну дешифрацію декількох команд, декілька паралельних конвейєрів команд, прогноз команд переходів і деякі інші методи.

Арифметико-логічний пристрій (або АЛП, ALU) призначений для обробки інформації відповідно до одержаної процесором команди. Прикладами обробки можуть служити логічні операції (типу логічного «І», «АБО», «Виключаюче АБО» і т.д.) тобто побітні операції над операндами, а також арифметичні операції (типу додавання, віднімання, множення, ділення і т.д.). Над якими кодами проводиться операція, куди поміщається її результат - визначається виконуваною командою. Якщо команда зводиться всього лише до пересилки даних без їх обробки, то АЛП не бере участь в її виконанні.

Швидкодія АЛП багато в чому визначає продуктивність процесора. Причому важлива не тільки частота тактового сигналу, яким тактується АЛП, але і кількість тактів, необхідних для виконання тієї або іншої команди. Для підвищення продуктивності розробники прагнуть довести час виконання команди до одного такту, а також забезпечити роботу АЛП на можливо більш високій частоті. Один з шляхів рішення цієї задачі полягає в зменшенні кількості виконуваних АЛП команд, створення процесорів із зменшеним набором команд (так звані RISC-процесори). Інший шлях підвищення продуктивності процесора - використовування декількох паралельно працюючих АЛП.

Що стосується операцій над числами з плаваючою крапкою і інших спеціальних складних операцій, то в системах на базі перших процесорів їх реалізували послідовністю більш простих команд, спеціальними підпрограмами, проте потім були розроблені спеціальні мікросхеми-обчислювачі - математичні співпроцесори, які замінювали основний процесор на час виконання таких команд. В сучасних мікропроцесорах математичні співпроцесори входять в структуру як складова частина процесора.

Регістри процесора є по суті елементами дуже швидкої пам'яті і служать для тимчасового зберігання різних кодів: даних, адрес, службових кодів. Операції з цими кодами виконуються гранично швидко, тому, в загальному випадку, чим більше внутрішніх регістрів, тим краще. Крім того, на швидкодію процесора сильно впливає розрядність регістрів. Саме розрядність регістрів і АЛП називається внутрішньою розрядністю процесора, яка може не співпадати із зовнішньою розрядністю.

По відношенню до призначення внутрішніх регістрів існує два основні підходи. Першого дотримується, наприклад, компанія Intel, яка кожному регістру відводить строго певну функцію. З одного боку, це спрощує організацію процесора і зменшує час виконання команди, але з іншою - знижує гнучкість, а іноді і уповільнює роботу програми. Наприклад, деякі арифметичні операції і обмін з пристроями вводу/виводу проводяться тільки через один регістр - акумулятор, внаслідок чого при виконанні деяких процедур може бути потрібно декілька додаткових пересилок між регістрами. Другий підхід полягає в тому, щоб всі (або майже всі) регістри зробити рівноправними, як, наприклад, в 16-розрядних процесорах Т-11 фірми DEC. При цьому досягається висока гнучкість, але необхідне ускладнення структури процесора. Існують і проміжні рішення, зокрема, в процесорі MC68000 фірми Motorola половина регістрів використовувалася для даних, і вони були взаємозамінні, а інша половина - для адрес, і вони також взаємозамінні.

Регістр ознак (регістр стану) займає особливе місце, хоча він також є внутрішнім регістром процесора. Інформація, що міститься в ньому, - це не дані, не адреса, а слово стану процесора (ССП, PSW - Processor Status Word). Кожний біт цього слова (прапор) містить інформацію про результат попередньої команди. Наприклад, є біт нульового результату, який встановлюється у тому випадку, коли результат виконання попередньої команди - нуль, і очищається у тому випадку, коли результат виконання команди відмінний від нуля. Ці біти (прапори) використовуються командами умовних переходів, наприклад, командою переходу у разі нульового результату. В цьому ж регістрі іноді містяться прапори управління, що визначають режим виконання деяких команд.

Схема управління перериваннями обробляє поступаючий на процесор запит переривання, визначає адресу початку програми обробки переривання (адреса вектора переривання), забезпечує перехід до цієї програми після виконання поточної команди і збереження в пам'яті (в стеку) поточного стану регістрів процесора. Після закінчення програми обробки переривання процесор повертається до перерваної програми з відновленими з пам'яті (із стека) значеннями внутрішніх регістрів. Докладніше про стек буде розказано в наступному розділі.

2.5.2. Функції пам'яті

Пам'ять мікропроцесорної системи виконує функцію тимчасового або постійного зберігання даних і команд. Об'єм пам'яті визначає допустиму складність виконуваних системою алгоритмів, а також в деякій мірі і швидкість роботи системи в цілому. Модулі пам'яті виконуються на мікросхемах пам'яті (оперативної або постійної). Все частіше у складі мікропроцесорних систем використовується флеш-пам'ять (англ. - flash memory), яка є енергозалежною пам'яттю з можливістю багатократного перезапису вмісту.

Інформація в пам'яті зберігається в комірках, кількість розрядів яких рівна кількості розрядів шини даних процесора. Звичайно вони кратні восьми (наприклад, 8, 16, 32, 64). Допустима кількість елементів пам'яті визначається кількістю розрядів шини адреси як 2N, де N - кількість розрядів шини адреси. Частіше за все об'єм пам'яті вимірюється в байтах незалежно від розрядності елемента пам'яті. Використовуються також наступні більш крупні одиниці об'єму пам'яті: кілобайт - 1024 байт (позначається Кбайт), мегабайт - 1 048 576 байт (позначається Мбайт), гігабайт (позначається Гбайт), терабайт - (позначається Тбайт) Наприклад, якщо пам'ять має 65 536 комірок, кожна з яких 16-розрядна, то говорять, що пам'ять має об'єм 128 Кбайт. Сукупність елементів пам'яті називається звичайно простором пам'яті системи.

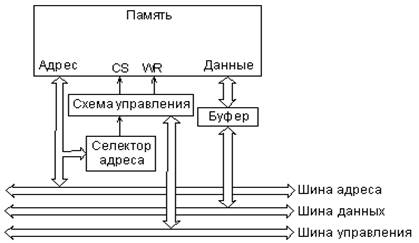

Для підключення модуля пам'яті до системної магістралі використовуються блоки сполучення, які включають дешифратор (селектор) адреси, схему обробки управляючих сигналів магістралі і буфери даних (мал. 2.18).

Оперативна пам'ять спілкується з системною магістраллю в циклах читання і запису, постійна пам'ять - тільки в циклах читання. Звичайно у складі системи є декілька модулів пам'яті, кожний з яких працює в своїй області простору пам'яті. Селектор адреси якраз і визначає, яка область адрес простору пам'яті відведена даному модулю пам'яті. Схема управління виробляє в потрібні моменти сигнали дозволу роботи пам'яті (CS) і сигнали дозволу запису в пам'ять (WR). Буфери даних передають дані від пам'яті до магістралі або від магістралі до пам'яті.

В просторі пам'яті мікропроцесорної системи звичайно виділяються декілька особливих областей, які виконують спеціальні функції.

Пам'ять програми початкового запуску завжди виконується на ПЗП або флеш-пам'яті. Саме з цієї області процесор починає роботу після включення живлення і після скидання його за допомогою сигналу RESET.

Мал. 2.18. Структура модуля пам'яті.

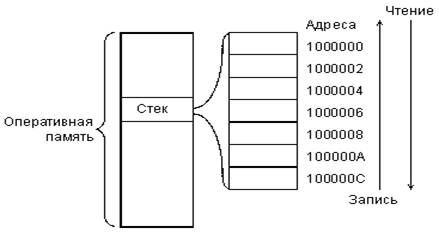

Пам'ять для стека або стек (Stack) - це частина оперативної пам'яті, призначена для тимчасового зберігання даних в режимі LIFO (Last In - First).

Особливість стека в порівнянні з іншою оперативною пам'яттю - це заданий і незмінний спосіб адресації. При записі будь-якого числа (кода) в стек число записується за адресою, визначуваною як вміст регістра покажчика стека, попереднє зменшене (декрементоване) на одиницю (або на два, якщо 16-розрядні слова розташовані в пам'яті за парними адресами). При читанні із стека число читається з адреси, визначуваної вмістом покажчика стека, після чого цей вміст покажчика стека збільшується (інкрементується) на одиницю (або на два). В результаті виходить, що число, записане останнім, буде прочитано першим, а число, записане першим, буде прочитано останнім. Така пам'ять називається LIFO або пам'яттю магазинного типу (наприклад, в магазині автомата патрон, встановлений останнім, буде витягнутий першим).

Принцип дії стека показаний на мал. 2.19 (адреси елементів пам'яті вибрані умовно).

Хай, наприклад, поточний стан покажчика стека 1000008, і в нього треба записати два числа (слова). Перше слово буде записано за адресою 1000006 (перед записом покажчик стека зменшиться на два). Друге - за адресою 1000004. Після запису вміст покажчика стека - 1000004. Якщо потім прочитати із стека два слова, то першим буде прочитано слово з адреси 1000004, а після читання покажчик стека стане рівним 1000006. Другим буде прочитано слово з адреси 1000006, а покажчик стека стане рівним 1000008. Все повернулося до початкового стану. Перше записане слово читається другим, а друге – першим.

Мал. 2.19. Принцип роботи стека.

Необхідність такої адресації стає очевидною у вкладених підпрограм. Хай, наприклад, виконується основна програма, і з неї викликається підпрограма 1. Якщо нам треба зберегти значення даних і внутрішніх регістрів основної програми на час виконання підпрограми, ми перед викликом підпрограми збережемо їх в стеку (запишемо в стек), а після її закінчення витягнемо (прочитаємо) їх із стека. Якщо ж з підпрограми 1 викликається підпрограма 2, то ту ж саму операцію ми виконаємо з даними і вмістом внутрішніх регістрів підпрограми 1. Зрозуміло, що усередині підпрограми 2 крайніми в стеку (читаними в першу чергу) будуть дані з підпрограми 1, а дані з основної програми будуть глибше. При цьому у разі читання із стека автоматично дотримуватиметься потрібний порядок читаної інформації. Те ж саме буде і у разі, коли таких рівнів вкладення підпрограм набагато більше. Тобто те, що треба зберегти довше, записується глибше, а те, що треба зберегти на менший час - з краю.

В системі команд будь-якого процесора для обміну інформацією із стеком передбачені спеціальні команди запису в стек (PUSH) і читання із стека (POP). В стеку можна ховати не тільки вміст всіх внутрішніх регістрів процесорів, але і вміст регістра ознак (слово стану процесора, PSW). Це дозволяє, наприклад, при поверненні з підпрограми контролювати результат останньої команди, виконаної безпосередньо перед викликом цієї підпрограми. Можна також зберегти в стеку і дані, для того, щоб зручніше передавати їх між програмами і підпрограмами. В загальному випадку, чим більша область пам'яті, відведена під стек, тим більше свободи у програміста і тим більш складніші програми можуть виконуватися.

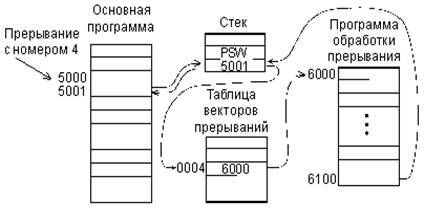

Наступна спеціальна область пам'яті - це таблиця векторів переривань.

Взагалі, поняття переривання досить багатозначне. Під перериванням в загальному випадку розуміється не тільки обслуговування запиту зовнішнього пристрою, але і будь-яке порушення послідовної роботи процесора. Наприклад, може бути передбачено переривання за фактом некоректного виконання арифметичної операції типу поділу на нуль. Або ж переривання може бути програмним, коли в програмі використовується команда переходу на якусь підпрограму, з якої потім послідує повернення в основну програму. В останньому випадку спільне з істинним перериванням тільки те, як здійснюється перехід на підпрограму і повернення з неї.

Будь-яке переривання обробляється через таблицю векторів (покажчиків) переривань. В цій таблиці в найпростішому випадку знаходяться адреси початку програм обробки переривань, які і називаються векторами. Довжина таблиці може бути досить великою (до декількох сот елементів). Звичайно таблиця векторів переривань розташовується на початку простору пам'яті (в елементах пам'яті з малими адресами). Адреса кожного вектора (або адреса початкового елемента кожного вектора) є номером переривання.

У разі апаратних переривань номер переривання або задається пристроєм, що запитав переривання (при векторних перериваннях), або ж задається номером лінії запиту переривань (при радіальних перериваннях). Процесор, одержавши апаратне переривання, закінчує виконання поточної команди і звертається до пам'яті в область таблиці векторів переривань, в той її рядок, який визначається номером запитаного переривання. Потім процесор читає вміст цього рядка (код вектора переривання) і переходить на адресу пам'яті, що задається цим вектором. Починаючи з цієї адреси пам'яті повинна розташовуватися програма обробки переривання з даним номером. В кінці програми обробки переривань обов'язково повинна розташовуватися команда виходу з переривання, виконавши яку, процесор повертається до виконання перерваної основної програми. Параметри процесора на час виконання програми обробки переривання зберігаються в стеку.

Хай, наприклад, процесор (рис.2.20) виконував основну програму і команду, що знаходиться в адресі пам'яті 5000 (умовно). У цей момент він одержав запит переривання з номером (адресою вектора) 4. Процесор закінчує виконання команди з адреси 5000. Потім він зберігає в стеку поточне значення лічильника команд (5001) і поточне значення PSW. Після цього процесор читає з адреси 4 пам'яті код вектора переривання. Хай цей код рівний 6000. Процесор переходить на адресу пам'яті 6000 і приступає до виконання програми обробки переривання, що починається з цієї адреси. Хай ця програма закінчується в адресі 6100. Дійшовши до цієї адреси, процесор повертається до виконання перерваної програми. Для цього він витягує із стека значення адреси (5001), на якій його перервали, і яким було в той момент PSW. Потім процесор читає команду з адреси 5001 і далі послідовно виконує команди основної програми.

Мал. 2.20. Спрощений алгоритм обробки переривання.

Переривання у разі аварійної ситуації обробляється так само, тільки адреса вектора переривання (номер рядка в таблиці векторів) жорстко прив'язана до даного типу аварійної ситуації.

Програмне переривання теж обслуговується через таблицю векторів переривань, але номер переривання вказується у складі команди, що викликає переривання.

Така складна, на перший погляд, організація переривань дозволяє програмісту легко міняти програми обробки переривань, розташовувати їх в будь-якій області пам'яті, робити їх будь-якого розміру і будь-якої складності.

Під час виконання програми обробки переривання може поступити новий запит на переривання. В цьому випадку він обробляється точно так, як і описано, але основною програмою вважається перервана програма обробки попереднього переривання. Це називається багатократним вкладенням переривань. Механізм стека дозволяє без проблем обслуговувати це багатократне вкладення, оскільки першим із стека витягується той код, який був збережений останнім, тобто повернення з обробки даного переривання відбувається в програму обробки попереднього переривання.

Відзначимо, що в складніших випадках в таблиці векторів переривань можуть знаходитися не адреси початку програм обробки переривань, а так звані дескриптори (описувачі) переривань. Але кінцевим результатом обробки цього дескриптора буде все одно адреса початку програми обробки переривань.

Нарешті, ще одна спеціальна область пам'яті мікропроцесорної системи - це пам'ять пристроїв, підключених до системної шини. Таке рішення зустрічається нечасто, але іноді воно дуже зручне. Тобто процесор дістає можливість звертатися до внутрішньої пам'яті пристроїв вводу/виводу або пристроїв підключених до системної шини, як до своєї власної системної пам'яті. Звичайне вікно в просторі пам'яті, що виділяється для цього, не дуже велике.

Вся решта частина простору пам'яті, як правило, має універсальне призначення. В них можуть розташовуватися як дані, так і програми (звичайно, у разі одношинної архітектури). Іноді цей простір пам'яті використовується як єдине ціле, без жодних меж. А іноді простір пам'яті ділиться на сегменти з програмно змінною адресою початку сегменту і зі встановленим розміром сегменту. Обидва підходи мають свої плюси і мінуси. Наприклад, використовування сегментів дозволяє захистити область програм або даних, та зате межі сегментів можуть утрудняти розміщення великих програм і масивів даних.

На закінчення зупинимося на проблемі розділення адрес пам'яті і адрес пристроїв вводу/виводу. Існує два основні підходи до рішення цієї проблеми:

- виділення в загальному адресному просторі системи спеціальної області адрес для пристроїв вводу/виводу;

- повне розділення адресних просторів пам'яті і пристроїв вводу/виводу.

Перший підхід хороший тим, що при зверненні до пристроїв вводу/виводу процесор може використовувати ті ж команди, які служать для взаємодії з пам'яттю. Але адресний простір пам'яті повинен бути зменшено на величину адресного простору пристроїв вводу/виводу. Наприклад, при 16-розрядній шині адреси всього може бути 64К адрес. З них 56К адрес відводиться під адресний простір пам'яті, а 8К адрес - під адресний простір пристроїв вводу/виводу.

Перевага другого підходу полягає в тому, що пам'ять займає весь адресний простір мікропроцесорної системи. Для спілкування з пристроями вводу/виводу застосовуються спеціальні команди і спеціальні строби обміну на магістралі. Саме так зроблено, наприклад, в персональних комп'ютерах. Але можливості взаємодії з пристроями вводу/виводу в даному випадку істотно обмежені в порівнянні з можливостями спілкування з пам'яттю.

2.5.3. Функції пристроїв вводу/виводу

Пристрої вводу/виводу обмінюються інформацією з магістраллю за тими ж принципами, що і пам'ять. Найістотніша відмінність з погляду організації обміну полягає в тому, що модуль пам'яті має в адресному просторі системи багато адрес (до декількох десятків мільйонів), а пристрій вводу/виводу звичайно має небагато адрес (звичайні до десять), а іноді і всього одна адреса.

Але модулі пам'яті системи обмінюються інформацією тільки з магістраллю, з процесором, а пристрої вводу/виводу взаємодіють ще і із зовнішніми пристроями, цифровими або аналоговими. Тому різноманітність пристроїв вводу/виводу набгато більше, ніж модулів пам'яті. Часто використовуються ще і інші назви для пристроїв вводу/виводу: пристрої сполучення, контролери, карти розширення, інтерфейсні модулі і т.д.

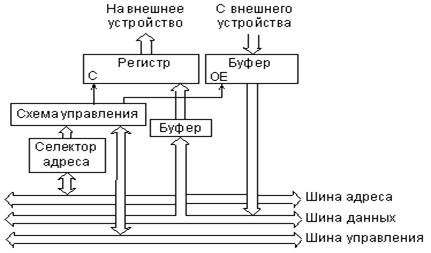

Об'єднують всі пристрої вводу/виводу загальні принципи обміну з магістраллю і, відповідно, загальні принципи організації вузлів, які здійснюють сполучення з магістраллю. Спрощена структура пристрою вводу/виводу приведена на мал. 2.21. Як і у разі модуля пам'яті, вона обов'язково містить схему селектора адреси, схему управління для обробки стробів обміну і буфери даних.

Самі найпростіші пристрої вводу/виводу видають на зовнішній пристрій код даних в паралельному форматі і приймають із зовнішнього пристрою код даних в паралельному форматі. Такі пристрої вводу/виводу часто називають паралельними портами вводу/виводу. Вони найбільш універсальні, тобто задовольняють потреби сполучення з великим числом зовнішніх пристроїв, тому їх часто вводять до складу мікропроцесорної системи як стандартні пристрої. Паралельні порти звичайно є у складі мікроконтролерів. Саме через паралельні порти мікроконтролер зв'язується із зовнішнім світом.

Вхідний порт (порт вводу) в найпростішому випадку є паралельним регістром, в який процесор може записувати інформацію. Вихідний порт (порт виводу) звичайно є просто однонаправленим буфером, через який процесор може читати інформацію від зовнішнього пристрою. Саме такі порти показані для прикладу на мал. 2.21>. Порт може бути і двонаправленим (вхідним/вихідним). В цьому випадку процесор пише інформацію в зовнішній пристрій і читає інформацію із зовнішнього пристрою за однією і тією ж адресою в адресному просторі системи. Вхідні і вихідні лінії для зв'язку із зовнішнім пристроєм при цьому можуть бути з'єднані порозрядний, утворюючи двонаправлені лінії.

Мал. 2.21. Структура найпростішого пристрою вводу/виводу.

При запиті з боку магістралі селектор адреси розпізнає адресу, приписану даному пристрою вводу/виводу. Схема управління видає внутрішні строби обміну у відповідь на магістральні строби обміну. Вхідний буфер даних забезпечує електричне узгодження шини даних з цим пристроєм (буфер може і бути відсутній). Дані з шини даних записуються в регістр по сигналу С і видаються на зовнішній пристрій. Вихідний буфер даних передає вхідні дані із зовнішнього пристрою на шину даних магістралі в циклі читання з порту.

Складніші пристрої вводу/виводу мають в своєму складі внутрішню буферну оперативну пам'ять і навіть можуть мати мікроконтролер, на який покладено виконання функцій обміну із зовнішнім пристроєм.

Кожному пристрою вводу/виводу відводиться своя адреса в адресному просторі мікропроцесорної системи. Дублювання адрес повинне бути виключено, за цим повинні стежити розробник і користувач мікропроцесорної системи.

Пристрої вводу/виводу крім програмного обміну можуть також підтримувати режим обміну по перериваннях. В цьому випадку вони перетворять поступаючий від зовнішнього пристрою сигнал запиту на переривання в сигнал запиту переривання, необхідний для даної магістралі (або в послідовність сигналів при векторному перериванні). Якщо потрібно використовувати режим ПДП, пристрій вводу/виводу повинен видати сигнал запиту ПДП на магістраль і забезпечити роботу в циклах ПДП, прийнятих для даної магістралі.

У складі мікропроцесорних систем, як правило, виділяються три спеціальні групи пристроїв вводу/виводу:

- пристрої інтерфейсу користувача (вводу інформації користувачем і виводу інформації для користувача);

- пристрої вводу/виводу для тривалого зберігання інформації;

- таймерні пристрої.

До пристроїв вводу для інтерфейсу користувача відносяться контролери клавіатури, тумблерів, окремих кнопок, миші, трекбола, джойстика і т.д. До пристроїв виводу для інтерфейсу користувача відносяться контролери світлодіодних індикаторів, табло, рідкокристалічних, плазмових і електронно-променевих екранів і т.д. В найпростіших випадках управляючих контролерів або мікроконтролерів ці засоби можуть бути відсутні. В складних мікропроцесорних системах вони є обов'язково. Роль зовнішнього пристрою в даному випадку відіграє людина.

Пристрої вводу/виводу для тривалого зберігання інформації забезпечують сполучення мікропроцесорної системи з дисководами (компакт-дисків або магнітних дисків), а також з накопичувачами на магнітній стрічці. Вживання таких пристроїв істотно збільшує можливості мікропроцесорної системи відносно зберігання виконуваних програм і накопичення масивів даних. В найпростіших контролерах ці пристрої відсутні.

Таймерні пристрої відрізняються від інших пристроїв вводу/виводу тим, що вони можуть не мати зовнішніх виводів для підключення до зовнішніх пристроїв. Ці пристрої призначені для того, щоб мікропроцесорна система могла витримувати задані тимчасові інтервали, стежити за реальним часом, рахувати імпульси і т.д. В основі будь-якого таймера лежить кварцовий тактовий генератор і багаторозрядні двійкові лічильники, які можуть перезапускати один одного. Процесор може записувати в таймер коефіцієнти розподілу тактової частоти, кількість відлічуваних імпульсів, задавати режим роботи лічильників таймера, а читає процесор вихідні коди лічильників. У принципі виконати практично всі функції таймера можна і програмним шляхом, тому іноді таймери в системі відсутні. Але включення в систему таймера дозволяє вирішувати складніші задачі і будувати більш ефективні алгоритми.

Ще один важливий клас пристроїв вводу/виводу - це пристрої для підключення до інформаційних мереж (локальних і глобальних). Ці пристрої поширені не так широко, як пристрої трьох перерахованих раніше груп, але їх значення з кожним роком стає все більшим. Зараз засоби зв'язку з інформаційними мережами вводяться іноді навіть в прості контролери.

Іноді пристрої вводу/виводу забезпечують сполучення із зовнішніми пристроями за допомогою аналогових сигналів. Це дуже зручно, тому до складу деяких мікроконтролерів навіть вводять внутрішні ЦАП і АЦП.